上一章我们讲到,stm32f10x系列处理器基于arm cortex-m3内核,按性能分为四个不同系列:基本型stm32f101系列,usb基本型stm32f102系列,增强型stm32f103系列,互联网型st32f105,stm32f107系列,统称为stm32f10x。以下我们以stm32f103系列为主,详细讲述一下其结构特点。

一、stm32f103微控制器外部结构

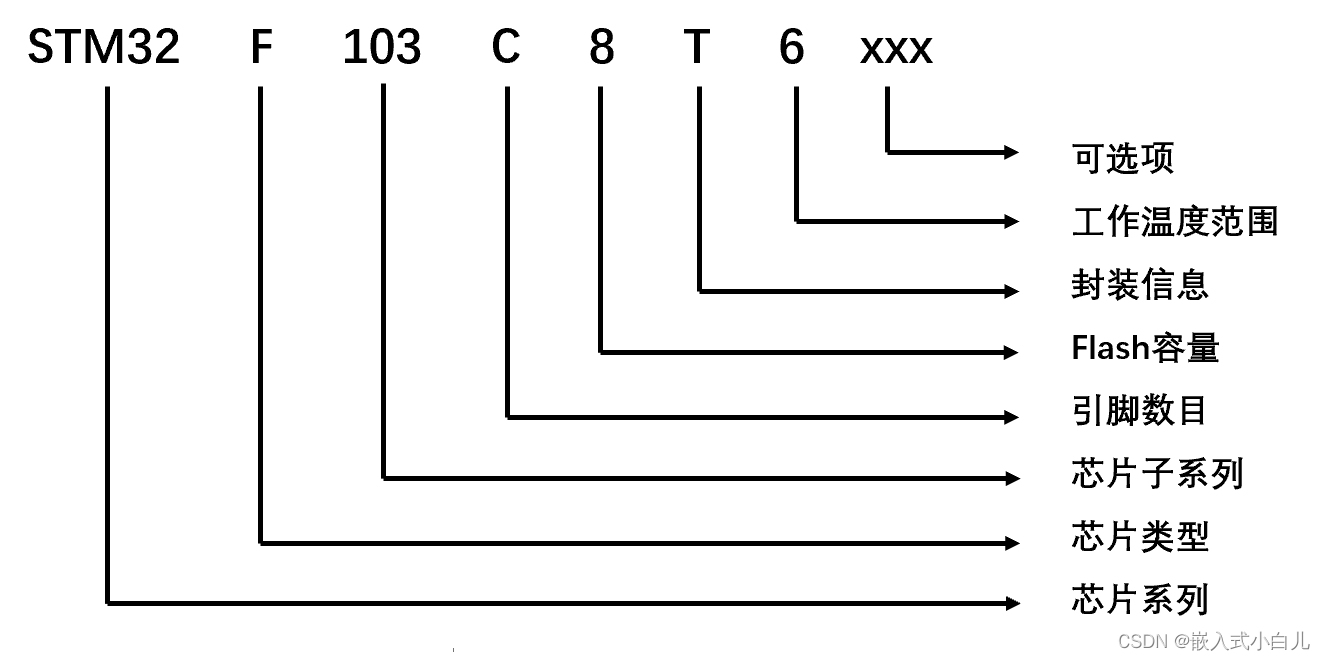

stm32f103系列芯片包含从36~144脚不同封装形式,不同的封装和丰富的资源使得stm32f103系列适用于多种场合,如医疗、pc外设,变频器等工业设备。 stm32系列命名遵循一定的规则,通过名字可以确定该引脚、封装、flash大小等信息。stm32命名规则如下所示,我们以市面上常见的stm32f103c8t6为主进行讲解:

(1)芯片系列:stm32代表st品牌cortex-mx系列内核(arm)的32位mcu。

(2)芯片类型:f-通用快闪,l-低电压(1.65~3.6v),w-无线系统芯片。

(3)芯片子系列:103—arm cortex - m3内核,增强型;050—arm cortex -m0内核;101—arm cortex-m3内核,基本型;102—arm cortex-m3内核,usb基本型;105—arm cortex-m3内核,usb互联网型;107—arm cortex-m3内核,usb互联网型、以太网型;215/217—arm cortex-m3内核,加密模块;405/407—arm cortex-m4内核,不加密模块等。

(4)引脚数目:r—64引脚,f—20引脚,g—28引脚,k—32引脚,t—36引脚,h—40引脚,c—48引脚,u—63引脚,o—90引脚,v—100引脚,q—132引脚,z—144引脚,i—176引脚。

(5)flash容量:b— 128kb(中容量),4—16kb(小容量),6—32kb(小容量),8—64kb(中容量),c—256kb(大容量),d—384kb(大容量),e—512kb(大容量),f—768kb(大容量),g—1mkb(大容量)。

(6)封装信息:t—lqfp,h—bga,u—vfqfpn,y—wlcsp。

(7)工作温度范围:6—-40°~85°(工业级),7—-40°~105°(工业级)

(8)可选项:此部分可以没有。

二、 stm32f103总线和存储器结构

2.1 总线结构

根据指令和数据所用的存储空间与总线形式的不同,可以把处理器分为冯·诺伊曼结构和哈弗结构。诺依曼结构的微处理器 指令和数据共用一个存储空间一条总线,这样内核在取时不能进行数据读写,反之亦然。哈弗结构的微处理器指令和数据存储在不同的存储空间,采用独立的指令总线和数据总线,可以同时进行取地址和数据读写操作,从而提高了处理器的运行性能。arm处理器采用的是哈弗结构。

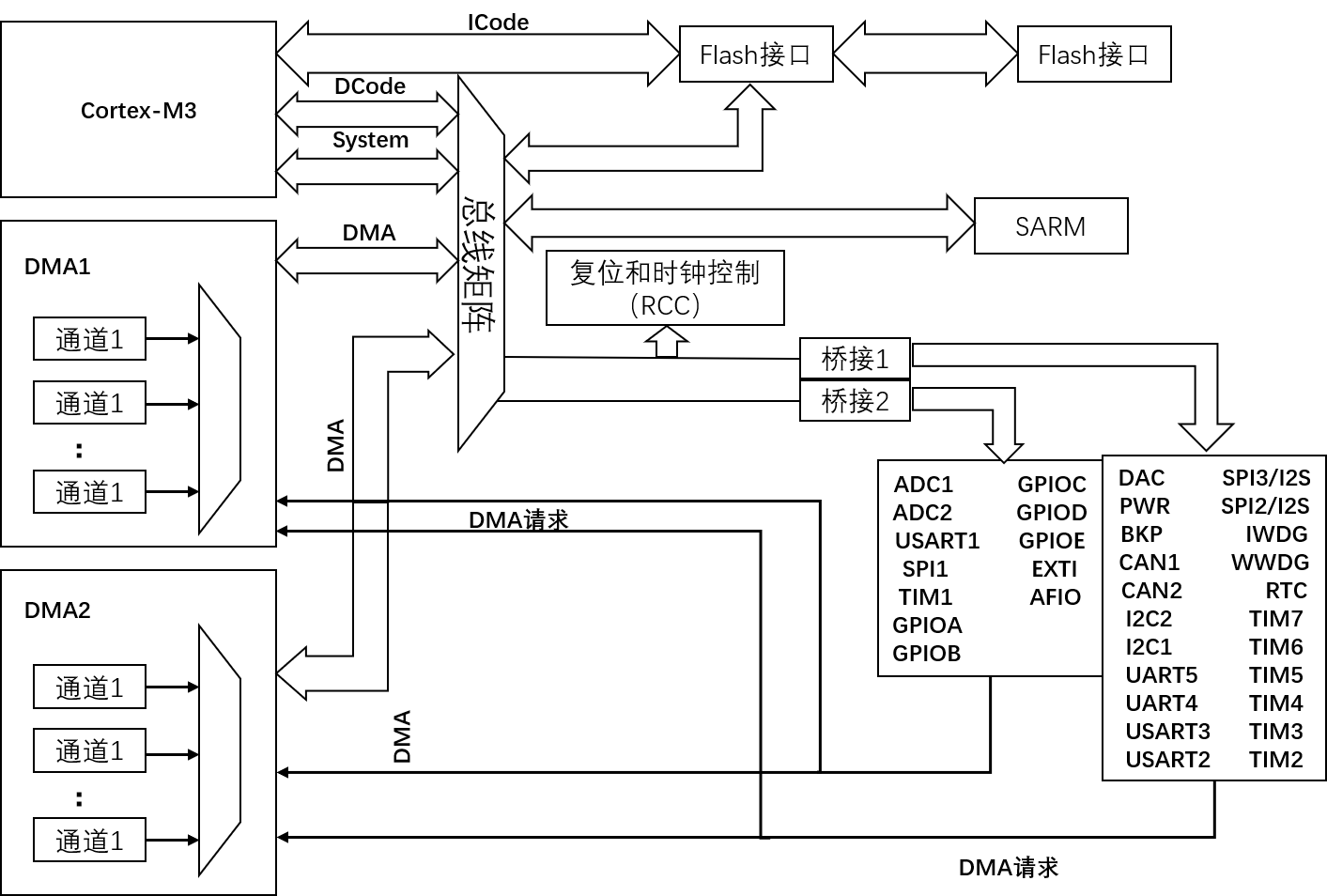

stm32f103的总线系统由驱动单元、被动单元和总线矩阵三部分组成,stm32f103总线系统如下图所示:

1. 驱动单元

(1)指令总线(icode):将cortex-m3内核的指令总线与flash指令接口相连接。取指操作在该总线上进行。

(2)数据总线(dcode):将cortex-m3内核的数据总线与flash数据接口相连接,用于常量加载和调试访问。

(3)系统总线(system):将cortex-m3内核的系统总线连接到总线矩阵,总线矩阵协调着内核和dma间的访问。

(4)直接内存访问总线(dma):将dma的ahb主机接口连接到总线矩阵,总线矩阵协调着cpu的dcode和dma到sram、闪存和外设的访问。

2. 被动单元

被动单元有3个,即内部sram、内部flash、ahb到apb桥。2个ahb/apb桥在ahb和2个apb总线之间提供完全同步的连接,apb1工作速度被限制在36mhz,apb2工作在全速72mhz。

3. 总线矩阵

dcode总线、system总线和通用dma总线通过总线矩阵与被动单元连接,总线矩阵分时轮换协调内核中数据总线、系统总线和dam总线之间的访问。为了允许dam访问,ahb外设通过总线矩阵连接到系统总线。

2.2 存储器结构和映射

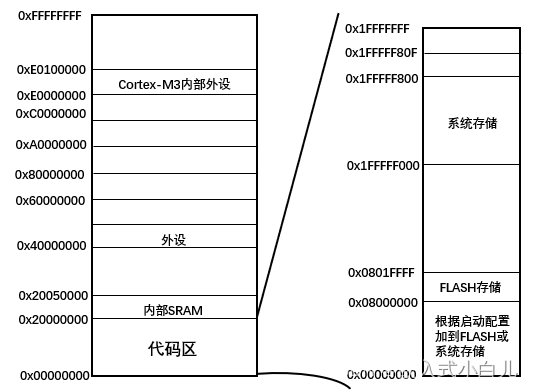

stm32f103的程序存储器、数据存储器、寄存器和io端口被组织到一个4gb的线性地址空间。数据自己以小段模式存放在存储器中。(小端格式:即低地址中存放的是数据的低字节,高地址中存放的是数据的高字节。)以stm32f103内存映射为例,其地址空间被分为8块,每块512mb。如下图所示:

2.3 位带

在stm32中,外设寄存器和sram都被映射到一个位带区中,使用下列术语来表示位带存储的相关地址:

(1)位带区:支持位带操作的地址区

(2)位带别名:位带区中位的别名,对别名的访问最终映射到位带区中位的访问上。

在位带区中,每一个比特(即每一位)都映射到别名地址区的一个字。该字只有最低位有效。当一个别名地址被访问时,会先把该地址变换成位带地址。对于读操作,读取位带地址中的一个字,再把需要的位右移到最低为并把最低为返回;对于写操作,把需要写的位左移至对应的位序号处,然后执行一个原子的“读-改-写”过程。

支持位带操作的两个内存区的范围是:

(1)0x20000000 ~ 0x200fffff(内部sram区中的最低1mb)。

(2)0x40000000 ~ 0x400fffff(片内外设区中的最低1mb).。

对于内部sram位带区的某个比特,记它所在字节地址为a,位序号为n(0≤n≤7),则该比特在别名区的地址为:

0x22000000 +((a-0x20000000)*8 +n)*4 = 0x2200000 +(a-0x20000000)*32+n*4

对于片内外设位带区的某个比特,记它所在字节的地址为a,序号为n(0≤n≤7),则该比特在别名区的地址为:

0x42000000 +((a-0x40000000)*8 +n)*4 = 0x4200000 +(a-0x40000000)*32+n*4

式中:4表示的是4个字节,8表示一个字节有8位。

发表评论