目录

异常的概念

arm的异常源

|

| |

| fiq | 快速中断请求 引脚有效 |

| irq | 外部中断请求 引脚有效 |

| reset | 复位电平有效 |

| software interrupt | 执行swi指令 |

| data abort | 数据终止 |

| prefetch abort | 指令预取终止 |

| undefined instruction | 遇到不能处理的指令 |

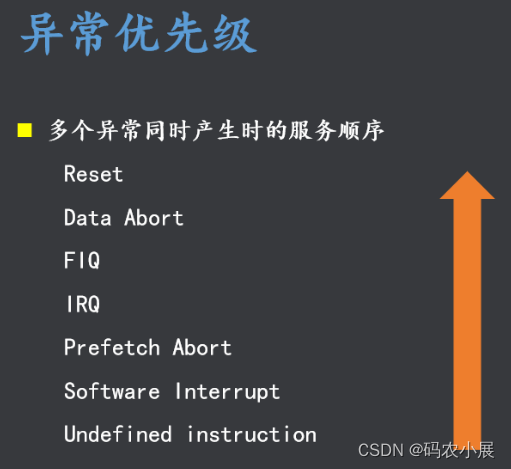

异常优先级

1、reset(重置)

处理器上电或者复位时发生的异常

2、data abort(数据中止)

数据访问错误时发生的异常,一般是与memory 误操作有关,如对不合法的内存地址、0地址写操作,或对一些memory 越界操作。或者指令不支持

3、fiq (快速中断)、irq (普通中断)

fiq 具有更高的优先级,即当 fiq 发生时,cpu 会在当前指令执行完成后立即响应 fiq 中断,而忽略其他 irq 中断。这使得 fiq 更适合处理紧急、实时性要求较高的中断。

4、prefetch abort(指令预取错误时发生的异常)

当cpu在执行指令时,发现指令缓存中没有下一条指令时,就会发生预取指中止异常。这种异常通常是由于程序中的错误或者硬件故障引起的。由于预取指中止异常的信息不够详细,因此很难定位和修复问题。

5、software interrupt(软件中断)

软件中断是一种由应用程序发起的中断,用于请求操作系统提供服务或执行某些操作。当应用程序需要访问受保护的资源或请求操作系统提供服务时,它会发出一个软件中断信号,这个信号会被cpu接收并暂时将控制切换到一个中断处理程序,内核中被中断挂起的进程将在中断被接受后恢复。软件中断可以被看作是同步事件,因为它是由应用程序主动发起的,而不是由外部设备触发的。

6、undefined instruction(执行了未定义指令时发生的异常)

undefined instruction异常是arm处理器中的一种异常类型,当cpu遇到不认识的指令时,就会触发该异常。在异常处理函数中,可以对该异常进行处理,例如打印debug信息或者进行其他操作。

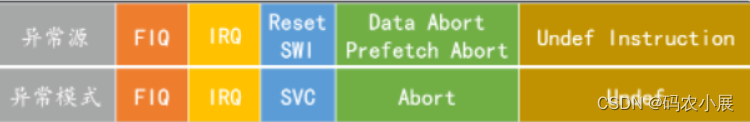

异常模式

异常处理的过程

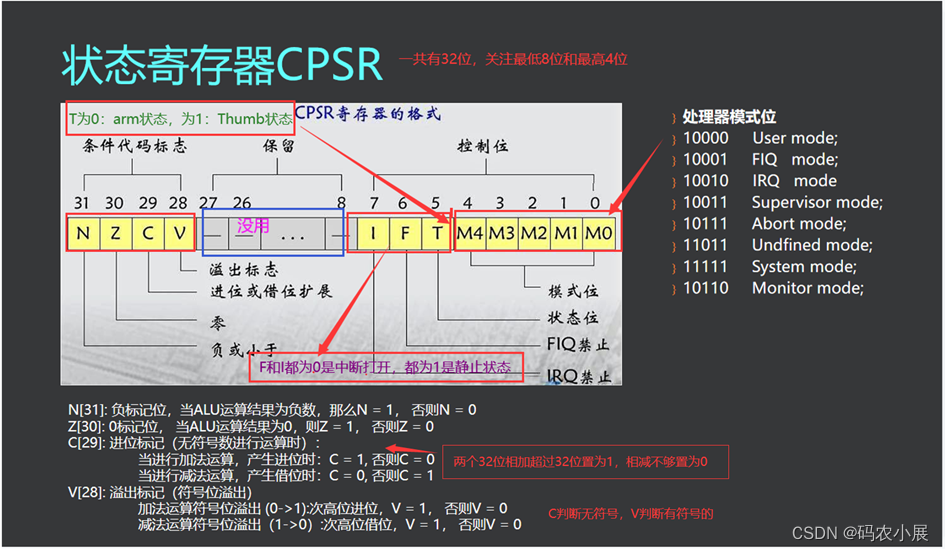

状态寄存器cpsr

发表评论