关于一个存储单元的容量的大小是多少,网上有人说是1bit,有人说是8bit。此篇用来给我自己一个满意的答案,也分享给需要的同学。先直接给出结论,解燃眉之疑惑:

l-bank中的基本存储单元的容量是若干个bit,对于sdram,就是芯片的位宽。而每个bit则是存放于单独的存储体中的,这些存储体是内存最小的存储单元。用硬盘中的簇与扇区来理解内存中的存储形式,扇区是硬盘最小的存储单元,而簇包含多个扇区,是数据交换的基本单位。类比,一个存储体是最小的存储单元,一个l-bank中的存储单元包含多个存储体,是数据交换的基本单位。

组织dram cell的方式,使得可以存储字节,而不仅仅是单个比特(从最小存储单元→基本存储单元)。每个基本储存单元的容量=数据线的位数(dq0-dqn)。【这里就是数据总线的位宽,因为一个rank上的存储颗粒共用地址线。】

【 如果上面这段总结没看懂,请先看我关于模组结构的博客,然后再阅读本篇剩余的内容。连接:http://t.csdn.cn/ynoqk】

1 bit 数据的读写

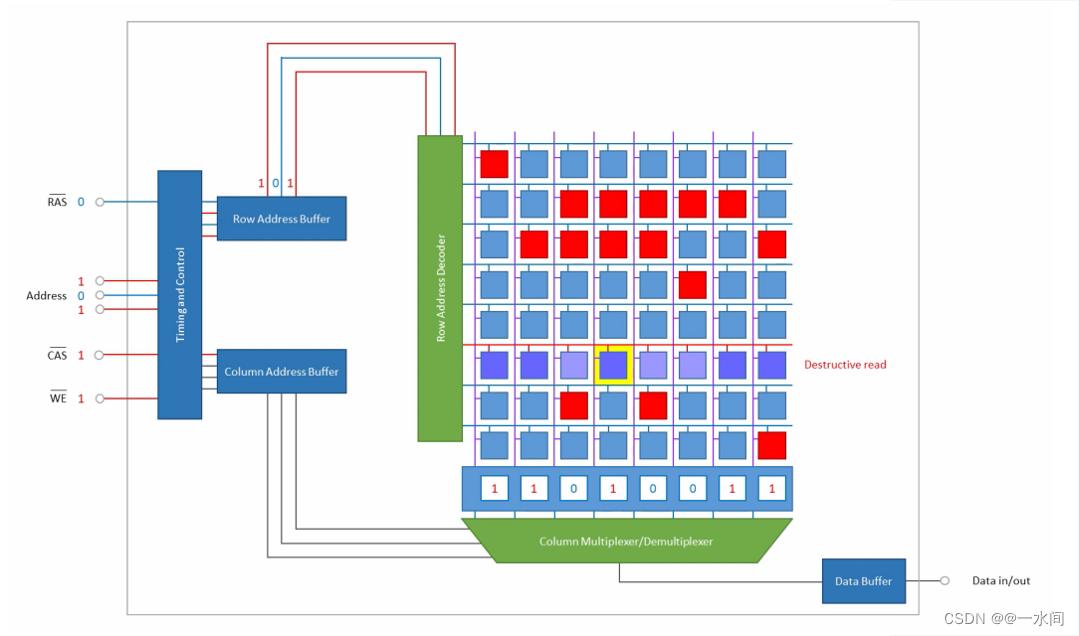

为了读取某特定cell存储的值,必须先读取整行。同样,如果要改变一个cell的值,必须整行读取,然后再重新写回。以8行8列的存储阵列为例,读取并输出一个特定cell中的数据二进制1时的步骤:

- 位线预充电,充电到大约dran供电电压的一半;

- 内存控制器将行地址加载到地址针脚上,并选通行地址缓存器(低电平),该步骤一旦开始,就会触发一整个读取周期。位线此时已经断离预充电电路,然后行地址被解码,解码器(decoder)拿到3bit地址,对应的字线被选中,整行cell的值被锁存到感应放大器中。

【因为整行cell中,存储了1的电容器会部分放电,存储了0的电容器会部分充电,所以读取一整行是一个破坏性的操作。】

- 然后列地址加载到地址针脚,通过列地址缓存器(低电平),列地址被锁存到列地址缓存器,多路器(column multiplexer)使用这个列地址从感应放大器中选择对应列的值输出。

【地址缓存的锁存器(row/column address buffer)用于暂存行地址或列地址(图中是分开的)。address是地址复用的,使用存储地址多路技术,行列地址缓存器允许行地址和列地址分别地输入到存储模块。】

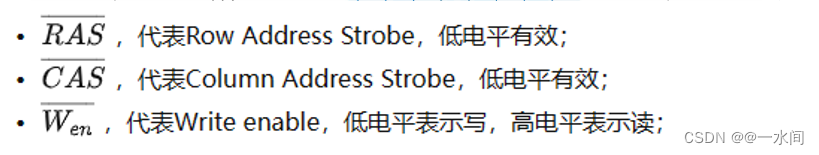

- 然后二进制1直接传向数据缓存器(data buffer)。行地址选通停用,向外输出的数据可在数据针脚中得到。破坏性地读取,使得cell被读取后必须重新写入,读取周期的最后一步是利用感应放大器中锁存的值刷新该行。

- 列地址选通停用,字线也断开,数据不再输出。之后是位线被预充电,为下一个运行周期做好准备。

【读取并输出cell中的值,需要有设置于每条位线末端的sense amplifier(感应放大器),其任务是探测某行cell上的存储值,锁存并将值重新写回。】

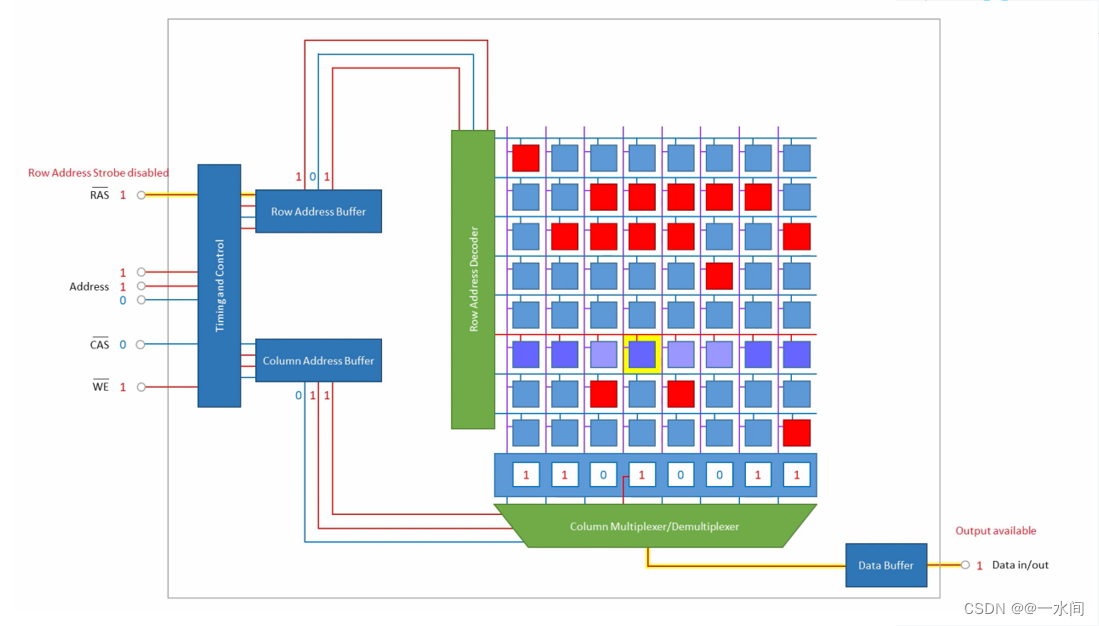

8 bit 数据的读取

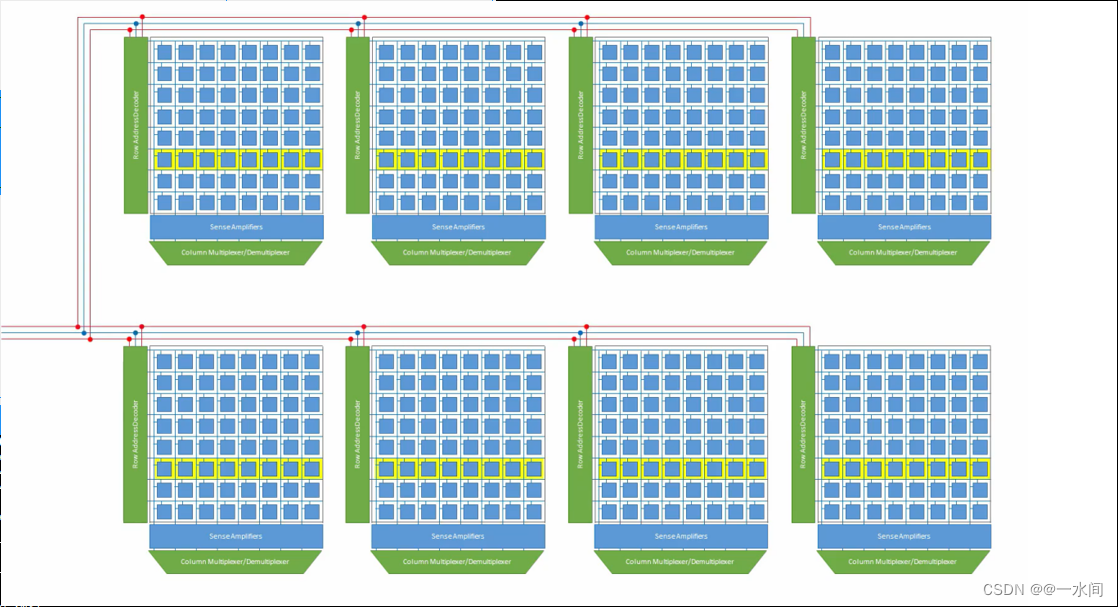

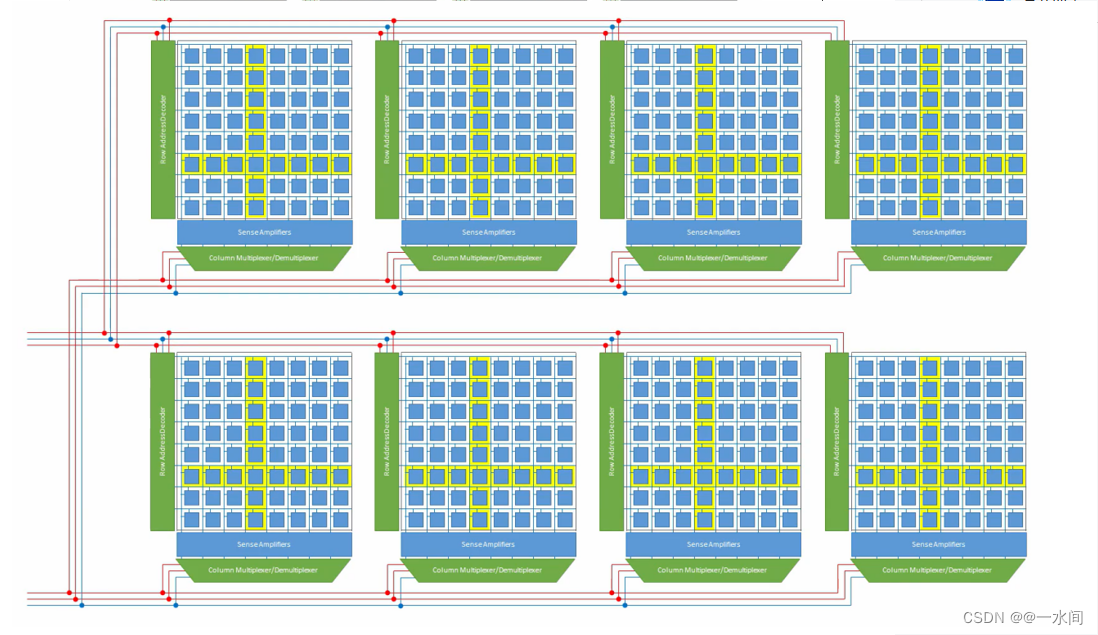

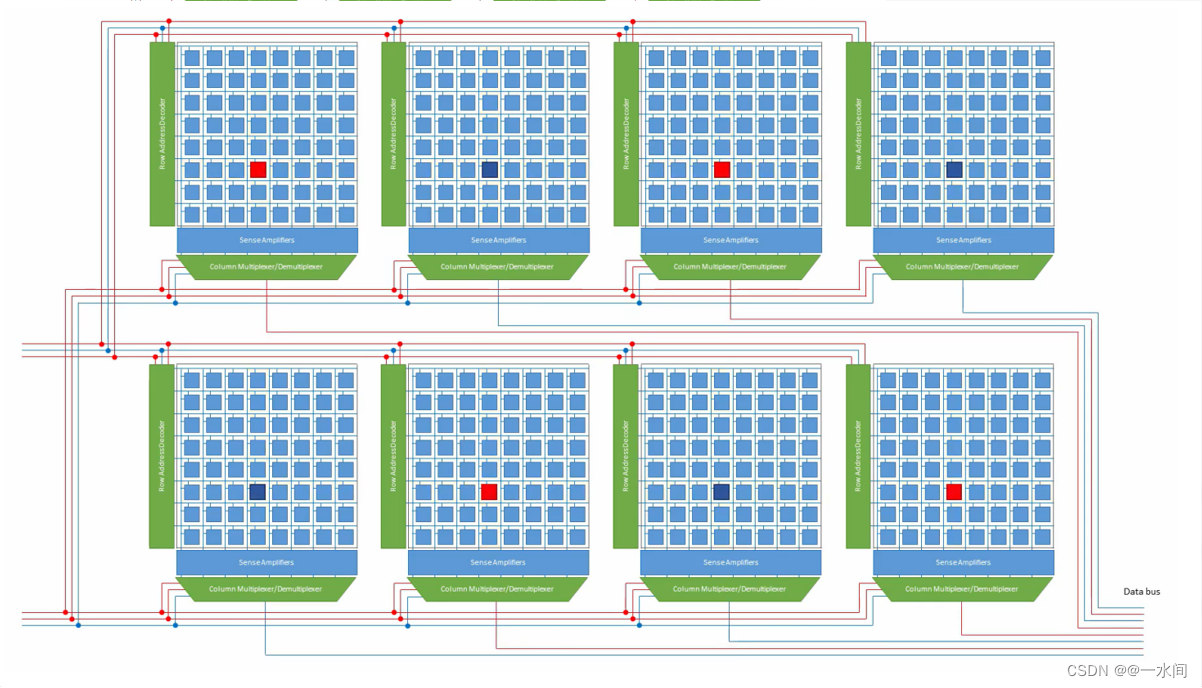

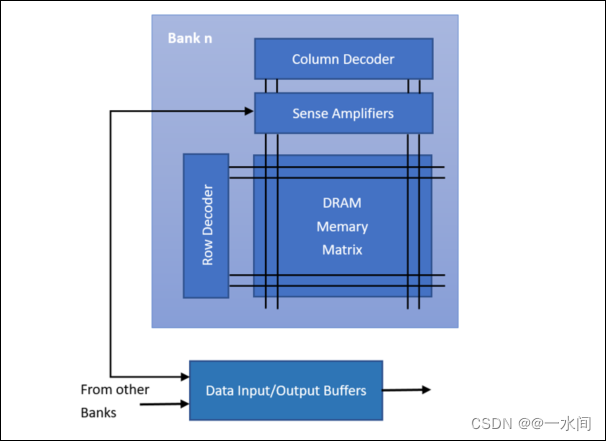

一个存储阵列(arrays)一次只能读取或写入一个二进制值。读取和写入一个字节的数据需要8个存储阵列,这样一组共享行列地址的的存储阵列称为一个bank(应该是l-bank)。每个阵列有自己独有的支持电路、解码器、感应放大器、多路器和分路器。

- 每个阵列的解码器都会被馈入相同的地址,当一个行地址被触发,8个阵列中的同一字线被选中(图下)。

- 每个阵列中多路器和分路器都被馈入相同的地址,当列地址被触发,每个阵列的同一个位线被选中。

- 每个阵列都连接到8线总线的一条上,在不同的阵列中,同一位置的cell上的二进制值可以被同时读取或写入(数据线是并联的),如此便能读取或写入一整个字节的数据。

基本信号线

实际中,操作一个存储单元需要一组信号,包括:cs#(片选信号,选择rank)、bank地址线(选择bank)、ras#(行选)、cas#(列选)、数据线、command命令(read/write)。

1、首先,内存控制器要先确定一个rank,即一个bank芯片结合。所以要有一个片选信号。

2、 然后是对所有被选中的rank进行统一的bank的寻址。比如,sdram中bank的数量为4个,那么就需要2个bank地址信号(22=4)。

3、 最后是对被选中的bank进行统一的行/列(存储单元)寻址。地址线数量要根据芯片的组织结构分别设计了。在相同容量下,行数不变,只有列数会根据位宽的变化而变化,位宽越大,一个rank中的rank数越多,每个bank的存储单元越少,则列数越少。

4、 找到了存储单元后,被选中的芯片就要进行统一的数据传输,则需要有与位宽相同数量的数据i/o通道才行,所以肯定要有相应数量的数据线引脚。

需要注意的是,chip没有选择信号线,只有rank的信号选择。在rank被选中后,被选中的rank上的内存颗粒一起被选中。所以说,chip是并行读取数据的,而一个chip中其实包括了多个bank,但是一个chip上一次只有一个bank做读写操作。

在读写操作之前需要以行为单位激活(active)存储单元,所谓激活就是导通该行所有存储单元中的管子 m,将储能电容 cs 通过信号线 bitline 与感应放大器(sense amplifier)相连,感应放大器将电容中的电平放大至 dram 颗粒的 0(gnd)/1(vdd)电平。

在随后的读写操作中,放大器将数值传输到外部的数据 io 上(读操作),或者获取新数值写入存储单元(写操作),所谓写入新数值,即写入电平 1 时为电容充电,写入电平 0 即为电容放电。

【本篇学习资源来自网络,感谢广大网友的知识分享……】

发表评论