消息称 SK 海力士五层堆叠 3D DRAM 内存良率已达 56.1%

2024年06月24日

•

内存

• 我要评论

我要评论

业内人士透露 SK 海力士在 6 月 16 至 20 日在美国夏威夷举行的 VLSI 2024 峰会上发表了有关 3D DRAM 技术的最新研究论文,其五层堆叠的 3D DRAM 内存良率已达 56.1%。

6 月 24 日消息,韩媒 businesskorea 报道,业内人士透露 sk 海力士在 6 月 16 至 20 日在美国夏威夷举行的 vlsi 2024 峰会上发表了有关 3d dram 技术的最新研究论文。

在这篇论文中,sk 海力士报告其五层堆叠的 3d dram 内存良率已达 56.1%,实验中的 3d dram 展现出与目前 2d dram 相似的特性。

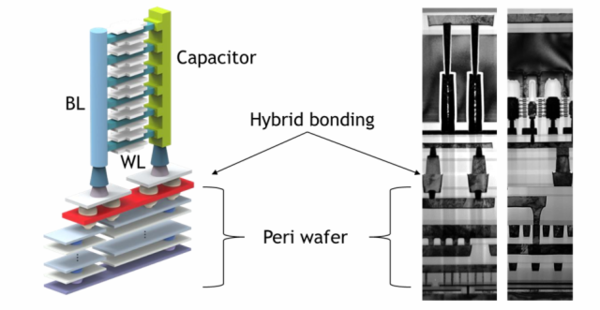

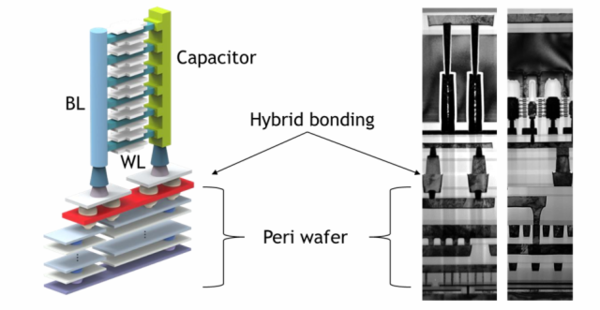

据介绍,与传统的 dram 水平排列内存单元不同,3d dram 垂直堆叠单元,可以在相同空间内实现更高的密度。

不过,sk 海力士指出,与 2d dram 的稳定运行不同,3d dram 表现出不稳定的性能特征,需要堆叠 32 到 192 层存储单元才能实现普遍应用。

代码网注意到,三星正在开发 16 层堆叠 3d dram,并在今年 3 月的 memcon 2024 展会上宣布计划在 2030 年左右实现 3d dram 产品商业化应用。

相关文章:

-

目前市面上大多旗舰级的内存产品都已经选用了海力士新推出的新m-die(3gb)颗粒,单条24gb套装48gb的组合,在性能和容量方面双双升级。宏碁掠夺者hermes冰刃24gb&t…

-

为了压制目前功耗越来越高的高端处理器,360水冷已经成为了大多数装机玩家的首选。在市场上诸多水冷散热器中选中一款令自己满意的产品,颜值和性能表现缺一不可。我这次入手的乔思伯tf2-…

-

-

-

-

型号为“TB375FC”的联想小新 Pad Pro 12.7 二代平板昨日通过国家 3C 认证,原装 45W 充电器;博主爆料显示其有望推出搭载舒视屏的版本。…

版权声明:本文内容由互联网用户贡献,该文观点仅代表作者本人。本站仅提供信息存储服务,不拥有所有权,不承担相关法律责任。

如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 2386932994@qq.com 举报,一经查实将立刻删除。

发表评论