「FPGA实现JPEG-LS图像压缩加速器:有损无损可配置,附工程源码和仿真文件」,FPGA实现JPEG-LS图像压缩加速器设计与仿真源码分享

2024-08-06 07:31 | 分类:硬件开发 | 评论:0 次 | 浏览: 290

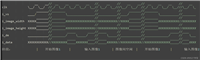

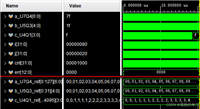

本设计使用system verilog语言设计了一个JPEG-LS图像压缩加速器,输入数据为8位的灰度图,输出数据为JPEG-LS图像压缩后...

二、FPGA实时图像处理(灰度转换、高斯滤波、二值化和边缘检测)

2024-08-06 07:30 | 分类:硬件开发 | 评论:0 次 | 浏览: 299

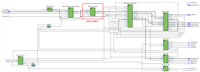

FPGA实时图像处理(灰度转换、高斯滤波、二值化和边缘检测)

使用Verilog实现SATA3.0协议的FPGA各模块详细指南

2024-08-06 07:26 | 分类:硬件开发 | 评论:0 次 | 浏览: 311

SATA3.0是SATA标准的第三代版本,提供了更高的传输速率和更强的性能。它采用串行通信方式,通过点对点连接实现主机与存储设备之间的数据传...

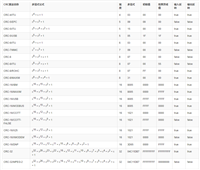

Xilinx 7系列 FPGA硬件知识系列(三)—— Bank划分及引脚定义

2024-08-06 07:25 | 分类:硬件开发 | 评论:0 次 | 浏览: 376

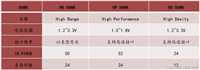

7系列的FPGA开始才有HP BANK和HR BANK,UltraScale FPGA有HP BANK、HR BANK和HD BANK,但并...

【FPGA开发/IC开发之时序约束最全面的归纳总结】时序路径基本概念及时序约束分析方法

2024-08-03 01:45 | 分类:硬件开发 | 评论:0 次 | 浏览: 372

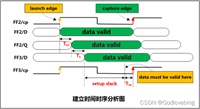

时序约束和时序分析在FPGA开发和数字IC设计中是重要的概念,本文主要阐述数字电路中时序路径基本概念和时序约束的基本分析方法

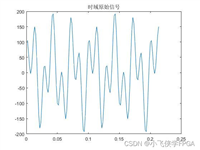

VIVADO中FFT核的使用(FPGA计算FFT和IFFT)

2024-08-03 01:44 | 分类:硬件开发 | 评论:0 次 | 浏览: 330

写这篇文章还是花了挺多的时间的,希望能对大家有所帮助,有什么问题欢迎一起讨论~奥利给。

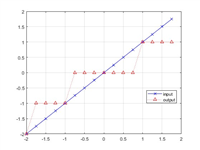

基于FPGA的数字信号处理(15)--定点数的舍入模式(6)向0取整fix

2024-08-03 01:43 | 分类:硬件开发 | 评论:0 次 | 浏览: 328

基于FPGA的数字信号处理(15)--定点数的舍入模式(6)向0取整fix

VMamba: Visual State Space Model论文笔记

2024-08-03 01:05 | 分类:硬件开发 | 评论:0 次 | 浏览: 345

VMamba论文阅读笔记,不包含实验部分

数字IC面经汇总(32篇)

2024-08-03 01:05 | 分类:硬件开发 | 评论:0 次 | 浏览: 347

为准备校招(自用),博主整理了往年数字IC前端(设计&&验证) && FPGA的面经,信息来自但不限于数字I...

FPGA - 以太网UDP通信(一)

2024-08-03 01:03 | 分类:硬件开发 | 评论:0 次 | 浏览: 336

以太网是现实世界中最普遍的一种计算机网络。以太网有两类:第一类是经典以太网,第二类是交换式以太网,使用了一种称为交换机的设备连接不同的计算机...

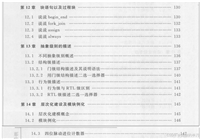

【数字IC/FPGA】书籍推荐(2)----《那些年,我们拿下了FPGA》

2024-08-02 01:48 | 分类:硬件开发 | 评论:0 次 | 浏览: 338

【数字IC/FPGA】书籍推荐(2)----《那些年,我们拿下了FPGA》

一文看懂JTAG基本知识

2024-08-01 00:15 | 分类:硬件开发 | 评论:0 次 | 浏览: 304

在此指令下,每个芯片的DR寄存器会延时一个时钟周期,那么我们发送一个数据后,检查延时多少周期收到数据,即可知道JTAG链上芯片的数量。JTA...

【机组】基于FPGA的32位算术逻辑运算单元的设计(EP2C5扩充选配类)

2024-08-01 00:15 | 分类:硬件开发 | 评论:0 次 | 浏览: 332

本文深入探讨了基于FPGA的32位算术逻辑运算单元的设计,特别针对EP2C5扩充选配类进行了详细分析。作者在文章中详细介绍了设计过程,着重于...

基于FPGA的数字信号处理(17)--定点运算的实现实例(饱和Saturate与四舍五入Round)

2024-08-01 00:14 | 分类:硬件开发 | 评论:0 次 | 浏览: 323

基于FPGA的数字信号处理(17)--定点运算的实现实例(饱和Saturate与四舍五入Round)

课程设计——基于FPGA的双向移位寄存器

2024-08-01 00:14 | 分类:硬件开发 | 评论:0 次 | 浏览: 298

本文使用verilog HDL语言设计双向移位寄存器,使电路受外部信号控制,实现数字信号的双向移位等功能,其电路设计模块主要分为三个部分,分...

【Verilog HDL 入门教程】 —— 学长带你学Verilog(基础篇)

2024-08-01 00:14 | 分类:硬件开发 | 评论:0 次 | 浏览: 378

Verilog HDL(Hardware Description Language)是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象...

FPGA学习笔记-1 FPGA原理与开发流程

2024-08-01 00:14 | 分类:硬件开发 | 评论:0 次 | 浏览: 342

简单介绍了FPGA发展历史、FPGA内部结构、FPGA开发流程、FPGA调试工具、Verilog语法等。