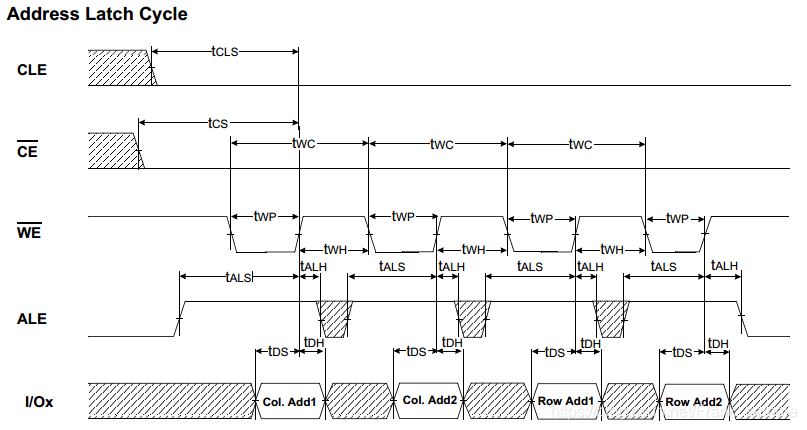

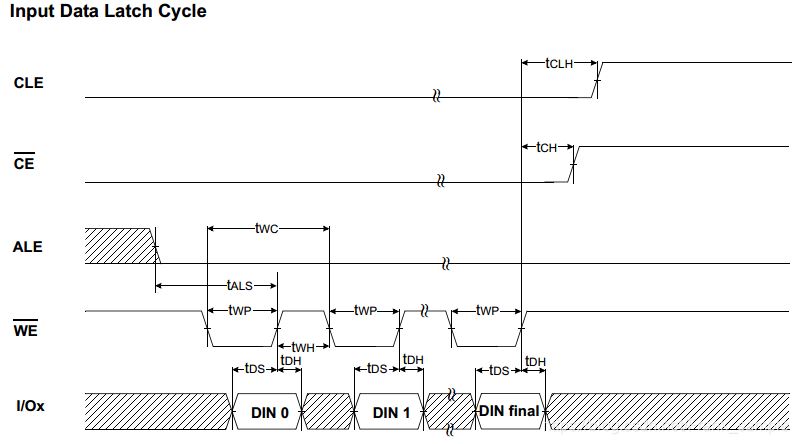

通过时序图看出,上面有很多时间参数,在设置nand flash控制器的时候,需要确认这些时间参数是否在合适的范围内,对于控制命令都是通过上面的几个基础命令组合而来。 flash的基本特性

data retention(数据保存力)是用于衡量写入nand flash的数据能够不失真保时间的可靠性指标,一般定义为在一定的温度条件下,数据在使用ecc纠错之后不失真保存在nand flash中的时间;影响data retention最大的两个因素是擦写次数和存储温度,通常情况下企业级ssd盘的data retention都是遵循jedec的jesd218标准,即40°c室温下,100%的pe cycle之后,在下电的情况下data retention时间要求达到3个月。

nand flash写入前必须擦除,block擦除1次之后再写入1次称为1次pe cycle,endurance(耐用性)用于衡量nand flash的擦写寿命的可靠性指标;endurance指的是在一定的测试条件下nand flash能够反复擦写数据的能力,即对应nand flash的pe(program/erase)cycle。

bit error rate(ber)指由于nand flash颗粒概率发生bit位翻转导致的错误,其中,rber(raw bit error rate)指没有经过ecc纠错时出现一个bit位发生错误的几率,rber也是衡量nand品质的一项指标。rber是nand自身品质的一个特性,随着pe次数的增加会变差,出现趋势呈指数分布,其主要原因是擦写造成了浮栅氧化层的磨损。

uber(uncorrectable bit error rate)指发生不可纠正ecc错误的几率,即一个纠错单元codeword内发生bit位翻转的位数超出ecc算法可纠能力范围的几率。

dwpd(diskful write per day)指每日写入量。ssd的成本随着dwpd增加而变高,未来ssd的趋势预测密集型当前已占50%,未来的占比会逐渐变大。

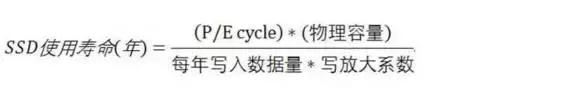

nand flash的寿命不等于ssd的寿命;ssd盘可以通过多种技术手段从整体上提升ssd的寿命,通过不同的技术手段,ssd盘的寿命可以比nand flash宣城寿命提高20%~2000%不等。

- nand flash的寿命主要通过p/e cycle来表征。ssd由多个flash颗粒组成,通过盘片算法,可以发挥有效颗粒寿命。影响ssd盘使用寿命关键因素主要包括下面因素:每年写入数据量,和客户的业务场景有关;

- 单个flash颗粒寿命,不同颗粒的p/e cycle不同

- 数据纠错算法,更强纠错能力延长颗粒使用寿命

- 磨损均衡算法,避免擦写不均衡导致擦写次数超过颗粒寿命

- over provisioning占比,随着op(预留空间)的增加ssd磁盘的寿命会得到提高。

flash的种类

flash通常分为raw nand和spi nand

raw nand tsop封装物料实物图

spi nand tsop封装

对于常见的nand flash所拥有的的引脚(pin)对应的功能如下:

- i/o0~i/o7:用于输入地址/数据/命令,输出数据

- cle:command latch enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置cle使能。

- ale:address latch enable,==地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ale使能。(地址锁存是由于数据和地址是复用同一些信号线或引脚的,一般来讲是由于工艺的要求,尽量节省成本和开支,那么在同一个引脚上就会出现两种信息:地址和数据,可处理器读的时候并不知道什么时候是地址,什么时候是数据,因此,需要一些专用的芯片把它们分开,用一些专用的信号联络线来区分这些信号,这就叫地址锁存)

- ce#:chip enanle,芯片使能,在操作nand flash之前,要先选中此芯片,才能操作。

- re#:read enable,读使能,在读取数据之前,要先使ce#有效。

- we#:write enable,写使能,在写取数据之前,要先使we#有效。

- wp#:write protect,写保护。

- r/b#:ready/busy/output,就绪/忙,主要用于在发送编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成。

- vcc:power 电源

- vss:ground 接地

- n.c:non-connection,未定义,未连接。

- 【小常识】在数据手册中,对于一些引脚的定义,有些字母上面带一横杠,那是说明此引脚/信号是低电平有效。

- 【为何需要ale和cle】地址锁存和数据锁存命令的设计是为了方便控制器区分当前i/o引脚输入的是数据还是命令,因为nand flash只有8个i/o,而且是复用,可以传数据也可以传命令。因此设计ale与cle引脚使能控制器做相应功能处理

- 【nand flash只有8个i/o引脚的好处】使用i/o复用可以减少芯片接口,也意味着使用此芯片的相关的外围电路会更加简化,避免繁琐的硬件连线。使用统一的8个i/o引脚的nand flash使用统一的接口、同样的时序、同样的命令,不会因为芯片的大小的改变或其他变化而影响。这样提高了系统的扩展性。

nand flash的特殊硬件结构

1、需要先擦除才能写入。nand flash可以读写一个page,但是必须要以block大小进行擦除。擦除操作就是让块中所有的bit变成1,从一个干净的“已擦除”状态的block重新开始,当里面的页变成0后,只有擦除整个块才能让这个页变成1.为了尽量减少擦除的次数,成熟的管理技术必不可少。

2、读、写干扰。nand flash的电荷非常不稳定,在读/写中很容易对相邻的单元造成干扰,干扰后会让附近单元的电荷脱离实际的逻辑数值,造成bit出错,因为阈值接近的关系,mlc相对slc来说更容易受到干扰。读取干扰指的是在读取某个page时,邻近的bit会受到升高电压的干扰,造成bit出错。写入干扰指的是,某个page在写入时,邻近bit的电压也被升高了,造成bit出错。相对写入干扰来说,读取干扰明显小的多。在读/写干扰中,可能造成某些bit被改变,结果造成数据出错。所以需要在返回数据给主机前,用ecc/edc算法来纠正这些bit的错误。随着闪存工艺的提升,同样大小的晶片上被封装入更多的单元,造成告饶越来越厉害,所以需要更强大的ecc/edc来纠正bit。

3、数据保存期限。数据保存期指的是当完全断电后,数据能在nand flash中保存多久。nand单元必须保存一个稳定的电压水平,来保证数据是有效的。典型的slc一般为20年。电荷从悬浮门里漏出,这叫做电子迁移,当随着时间的流逝,电核泄漏到一定程度,改变了nand单元里悬浮门的电压对应的逻辑值,这样就造成了bit出错。数据保存期会随着擦写次数的增加而明显降低,mlc的数据保存期明显会比slc少,而且更容易被 干扰。

4、坏块。nand flash中有两种坏块类型:出厂坏块,由于为了保证量产和控制成本,出厂的nand flash某些就会有坏块,厂商保证slc出厂坏块低于2%,mlc出厂坏块低于5%。积累坏块,在多次的写入/擦除循环中,某些nand单元的电荷电压被永久性的改变了,那就意味着包含这个nand单元不再可用。所以固态硬盘需要有坏块管理才能使用,主控制器用坏块表来映射出厂坏块和积累坏块到坏块区内,出厂时,颗粒的第一个块block 0厂商会保证是可用的。(至少ecc后可用)

5、擦写次数限制。造成nand flash有擦写次数限制的主要有2个因素,电荷被困在氧化层,不能进入悬浮门;或是氧化层结构被破坏。

如图,一旦氧化层损坏到达一定程度,造成电荷越来越难在p-substrate和悬浮门之间交流。电荷被困在氧化层造成悬浮门中的电压到达不了阈值,所以说这个nand单元就要被放入坏块区了。当前主流slc的p/e为10万次,50nm mlc为1万次,3xnm的mlc为5000次。到了这个数值并不意味着不能使用了,这只是代表平均寿命,也就是说到了这个数值后,坏块会开始大量增加。随着工艺的提升,ecc的要求越来越高,50nm的slc颗粒,三星对顶1bit ecc的就够了,而50nm mlc需要4bit ecc,到了3xnm要求达到24bit ecc。

ecc

影响nand flash稳定性和耐久度的一个主要因素就是ecc能力,目前最常用的三种算法是:

- reed-solomon

- hamming

- bch(bose,ray-chauduri,hocquenhem)

不管是任何ecc算法,任何主控,检测错误的方式都是相同的:

不管是任何ecc算法,任何主控,检测错误的方式都是相同的:

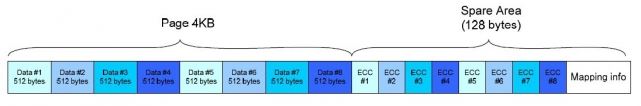

- 1、每当一个page写入nand flash,数据会通过ecc引擎,创造独特的ecc签名。

- 2、数据和对应的ecc签名都存放在nand flash里,数据存放在数据区,ecc签名存放在sa区。

- 3、当需要读取数据时,数据和ecc签名一起被送往主控制器,此时新的ecc签名被生成。

- 4、此时主控把2个签名对照,如果签名相同,说明数据没有错误,数据就会被送往主机。如果签名不同,数据就会先放在主控里,而不是直接送往主机。

某些主控会把改正后的数据再次回写闪存,另一些则不会,因为谁也不知道下次读取会不会再出错。ecc的能力直接关系到nand flash的耐久度,数据保存期。当nand flash的p/e数到了之后,错误数会越来越多,ecc弱的直接就报坏块并标记退休,如果ecc能力足够强,就能够挖掘出flash的所有潜力。

闪存内部原理

闪存的内部存储结构是金属-氧化物-半导体-场效应管(mosfet):源极、漏极和栅极,其工作原理与场效应管类似,都是电压利用控制源极和漏极之间的通断。闪存是双栅极结构,在栅极和硅衬底之间还有一个浮置栅极,浮置栅极是有氮化物夹在二氧化硅材料之间构成。

对闪存单元的编程:控制栅极去充电,对栅极加压,使得浮置栅极存储的电荷越多,超过阈值,就表示0;对闪存单元的擦除,即对浮置栅极进行放电,低于阈值,就表示1。

nand flash发展历程

- 诞生阶段(20 世纪 80 年代):

1987 年,时任日本东芝公司工程师岡本成之提出了 2d nand 技术,这是 nand flash 的起源。当时,东芝虽然占据了市场先机,但战略重心偏向 dram 市场,一定程度上忽略了 nand flash 的发展潜力。随后,英特尔和三星等公司也迅速加入该领域,推出了自己的 2d nand 产品。在这一阶段,nand flash 主要应用于一些特定的电子设备,如数字电话答录机等。

- 小型闪存卡兴起阶段(20 世纪 90 年代 - 21 世纪初):

随着数码摄影的普及,一系列小型闪存卡应运而生,包括 pcmcia(pc 卡)、compactflash、smartmedia、multimediacard(mmc)和 securedigital(sd)卡等,这些小型闪存卡的存储介质主要是 nand flash。这使得 nand flash 的应用范围得到了极大的扩展,市场需求也开始快速增长。

- 市场扩张阶段(21 世纪初 - 2010 年代):

随着 nand flash 成本的不断降低,其应用范围进一步扩大。从数码相机扩展到了 usb 闪存驱动器,进而取代了软盘和可写 cd 等传统存储设备。同时,音频播放设备从传统的磁带和 cd 播放器转变为 mp3 播放器,也推动了 nand flash 的需求增长。在这一时期,nand flash 逐渐成为了主流的存储技术之一,市场规模不断扩大。

- 3d nand 技术发展阶段(2010 年代 - 至今):

技术概念

提出 2007 年,东芝推出 bics 类型的 3d nand,标志着 nand flash技术从二维平面堆叠向三维立体堆叠的转变。这种技术通过在垂直方向上堆叠存储单元,大大提高了存储密度,为 nand flash的进一步发展提供了新的方向。

商业化量产

2013 年,三星推出第一代 v-nand(三星自称 3d nand 为 v-nand)闪存并投入量产,虽然该款堆叠层数仅为

24 层,但在当时却打破了平面技术的瓶颈,并使 3d nand 从技术概念推向了商业市场。

层数不断增加

从 2014 年开始,各大厂商纷纷推出更高层数的 3d nand 产品。例如,三星陆续推出了 32 层、48 层、64层、96 层、128 层、176 层等不同层数的 v-nand;sk 海力士按照 48 层、72 层 / 76 层、96 层、128 层、176 层、238 层的顺序陆续推出闪存新产品;美光也在不断提高其 3d nand 的层数。

技术持续演进

在 3d nand 技术发展的过程中,厂商们还在不断改进和优化技术,以提高存储性能、降低成本。例如,长江存储自研出了xtacking 架构,大幅度提高了存储密度。

发表评论