1 ddr3概述

ddr,名称:double data rate sdram,全称:双倍数据率同步动态随机存储器。允许在时钟的上升沿,下降沿传输数据,其主要作用是为了和cpu频率同步,进而大大提高数据传输效率。本工程使用的为ddr3 sdram,它具备更低的工作电压(1.5v),240线接口、支持8bit预读;

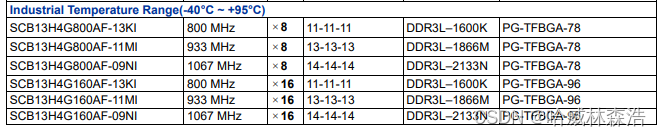

项目所使用的芯片为紫光国芯scb13h4g160af-11mi,该芯片容量为512gb(4gbit),最大支持933mhz时钟输入。

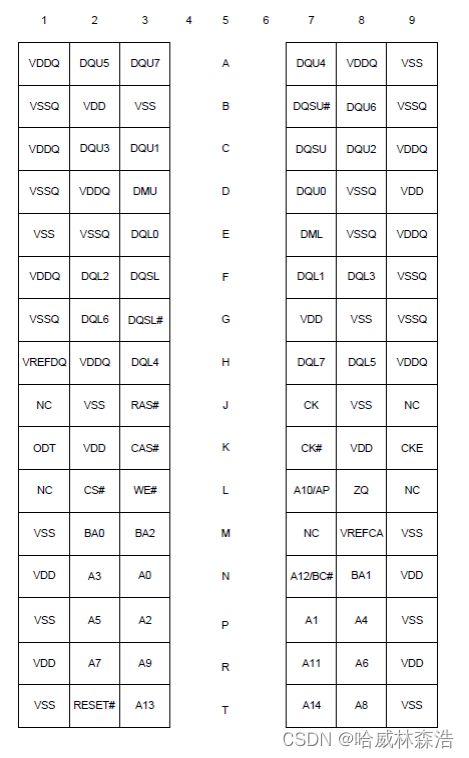

2 ddr3管脚介绍

ddr3管脚根据不同的功能可以分为:数据组、地址组、控制组和电源组。如图上所示,共96个管脚。

2.1数据组

dq[15:0]:双向信号,16位数据总线; dqs /dqs: 数据选通,用于数据同步,读时是输出,边缘与读出的数据对齐。写时是输入。中心与写数据对齐。 dm:输入数据掩码。

2.2地址组

ba0~ba2:bank地址选通; a0~a14:地址线;

2.3控制组

ck,/ck:差分时钟输入; cke:时钟使能信号; /cs:片选信号; /ras:行地址选通信号; /cas:列地址选通信号; /we:读使能信号; odt:片上终端使能信号。ddr3芯片数据组是有片上端接的,无需外部端接,而控制信号和地址位保证信号完整性需要端接匹配; zq:校准管脚,下拉240ω电阻到vssq。

2.4电源组

vddq:dq供电,1.283v到1.45v或者1.5v±0.075v: vssq:dq的地; vdd:电源电压,1.283v到1.45v或者1.5v±0.075v: vss:电源地; verfdq:数据参考电压,电压为vdd/2; verfca: 控制、命令和地址参考电压,电压为vdd/2;

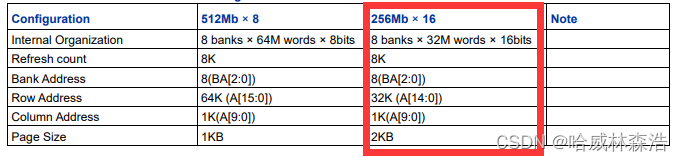

3 ddr3寻址及容量计算

将ddr芯片在逻辑上分为8个bank,每个bank可以理解为一个二维数组bool array。row/column就是指示这个二维数组里的坐标。读写某个bank,需要先指定一个行(row),再指定一个列(column)。

如图,row address = 15bit,column address = 10bit,bank address = 3bit,总的存储单元:2^15×2^10×2^3=2^28=256m,总的容量为:256m×16bit = 512mb(4gbit)。

4 ddr3引脚分配

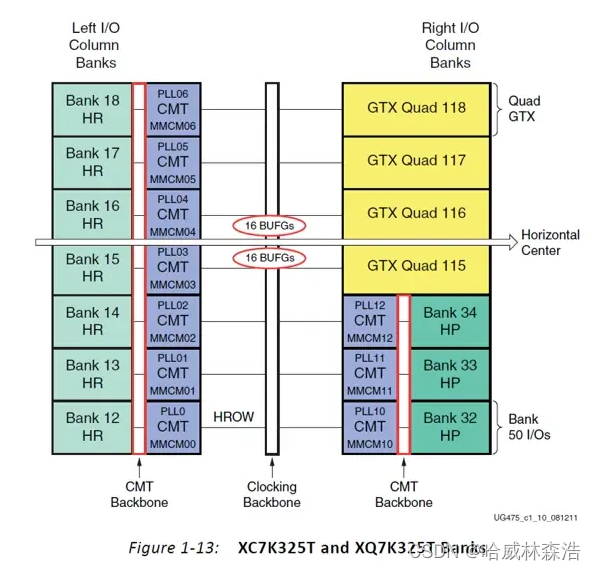

4.1 7系列fpga引脚划分

7系列的fpga开始才有hp bank和hr bank,ultrascale fpga有hp bank、hr bank和hd bank,但并不是一个fpga中会同时包含hp/hr/hdbank。

hp:high performance,应用于高速场景,比如ddr或其他高速差分线(不是gtx)

hr:high range,应用于宽范围i/0,最高能够支持到3.3v的电压。

hd:high density,应用于低速i/o的场景,最高速率限制在250m以内,最高电压也是支持到3.3v。

如图,ddr的引脚分配一般在hpbank上,也就是bank32,33,34.

4.1.1 用户bank

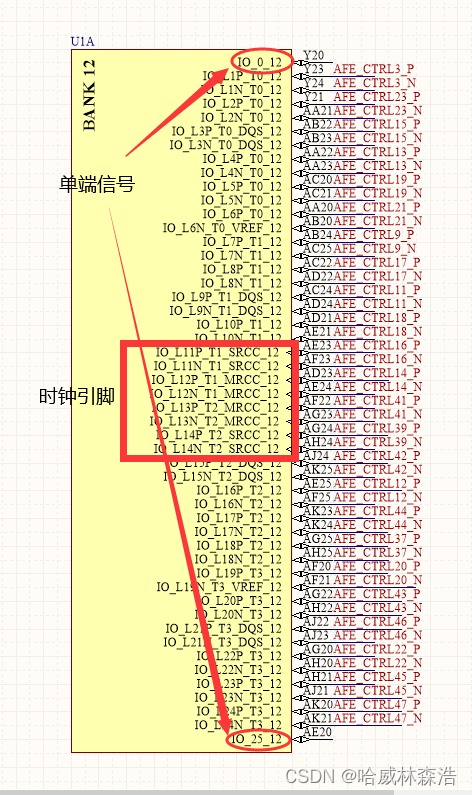

fpga的管脚按照bank进行划分,每个bank独立供电,以使fpga i/o适应不同电压标准,增强i/o设计的灵活性。每个用户bank包括50个i/o管脚,或者说24对差分对管脚,顶端和底端各一个单端管脚。

在上图中,红色圈住的是两个单端信号蓝色圈住的是时钟管脚,在不作为时钟输入时可以当作普通i/o使用。

4.2 ddr3引脚分配原则

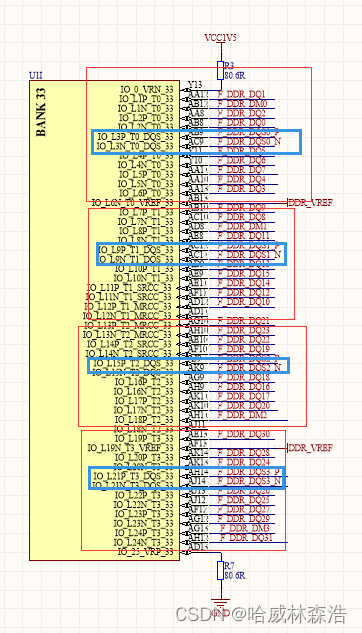

1.fpga的一个bank可以放置4个group的ddr3信号。 2.每个group包含1对dqs差分信号,8个数据信号,1个dm信号。其中dqs的位置是固定的,不能随意接,数据信号dq和dm在组内可以互换,注意要按组摆放。 3.时钟信号必须放置在同一差分对上。

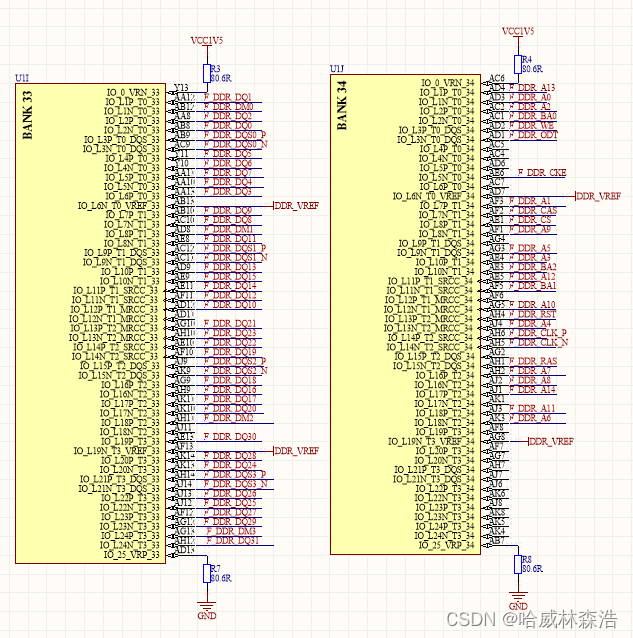

如图,t0,t1,t2,t3为bank33的4个组,分别用红色框圈了出来,蓝色框圈的为dqs信号,每一组的dqs都在固定位置。一个mig控制器最多支持的数据位宽为72bit,这些数据分布在3个bank上。其中地址、控制、时钟信号必须在中间bank。比如使用7k325t的bank32,33,34,地址控制、时钟信号必须放置在bank33.

本项目的数据位宽为32bit,故选用了2个bank,分别是33,34。他的引脚分配如上图所示。

发表评论